## Program analyzes all-resistive dc circuits

by Mark Jong Wichita State University, Wichita, Kansas

Networks that are strictly resistive can be analyzed easily and quickly for dc conditions with a brief but effective computer program written in Basic. The circuit to be analyzed can also contain active devices, provided those devices can be represented by only resistive elements and voltage-dependent sources.

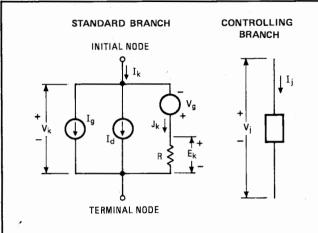

The standard circuit branch allowed by the program is shown in Fig. 1, along with the program listing. Nodes may be numbered in any order with consecutive integers beginning with zero. (The program always assumes that node 0 is the reference node.) Branches may also be numbered in any order with consecutive integers, but this set of numbers must begin with the number one.

The program first asks to know the number of nodes minus one, and then it requests the number of branches.

1. De circuit analysis. Computer program, which is written in Basic, is useful for a speedy dc analysis of small resistive networks. The definitions for a standard circuit branch and the program listing itself are given here. Dependent sources must be voltage-controlled.

(A question mark is typed after each request.) The user responds by typing in the data requested each time and pressing the RETURN key on his terminal.

After this preliminary input data is obtained, the program asks for the branch data by typing a question mark each time for each branch. In response, the user types in the data for each branch in a specific order and

$$\begin{split} & v_k, \, v_j = \text{branch voltages} \\ & I_k, \, I_j = \text{branch currents} \\ & E_k = \text{element voltage} \\ & J_k = \text{element current} \\ & v_g, \, I_g = \text{independent sources} \\ & I_d = g_m \cdot v_i \, (\text{voltage-controlled current source)} \end{split}$$

```

100

DIM AL7, 151, YL15, 151, EL151, IL151,

35Ø

MAT W=A*U

J[15], V[15], S[15], W[15, 7], U[15, 7]

MAT U=ZER[N,N]

360

PRINT "NUMBER OF NODES - 1 =";

MAT U=INV(W)

INPUT N

38Ø

MAT V=ZER[N]

PRINT "NUMBER OF BRANCHES =";

30 Ø

MAT V=A+S

INPUT B

400

MAT J=ZER[N]

MAT A=ZER[N,B]

MAT J=U+V

410

140

MAT Y=ZER[B, B]

PPINT

420

MAT E=ZER[B]

PRINT "NODE"," VOLTAGE"

150

430

MAT I=ZER[B]

FOR K=1 TO N

16Ø

440

PRINT K, JIKI

FOR K=1 TO B

450

170

INPUT B1, F1, T1, R, E(B1), I(B1), Y1, C1

460

188

NEXT K

190

IF F1=0 THEN 210

470

MAT V=ZER[B]

200

LET ALFI, BIJ=1

480

MAT W=ZER(B,N)

210

IF T1=0 THEN 230

490

MAT W=TRN(A)

220

LET ALTI, BIJ =- 1

500

KAT V=W*J

230

LET YIBI,BIJ=1/R

510

MAT J=ZER[B]

IF C1=0 THEN 260

MAT J=Y*V

LET Y[BI,CI]=YI

530

MAT J=J-S

260

NEXT K

540

PRINT

PRINT "BRANCH"," VOLTAGE"," CURRENT"," POWER"

270

MAT S=ZER[B]

552

275

MAT J=ZER[B]

FOR K=1 TO B

560

280

FOR K=1 TO B

PRINT K, V(K), J(K), V(K)*J(K)

57Ø

LET SIKJ=YIK,KJ*EIKJ

281

580

NEXT K

NEXT K

MAT U=V+E

28.2

59Ø

29Ø

MAT S=I+S

67.0

PRINT

PRINT "ELEMENT", " VOLTAGE", " CURRENT", " POWER"

295

MAT S=J-S

610

300

MAT W=ZER[E,N]

FOR K=1 TO B

628

310

MAT W=TRN(A)

LET J[K]=Y[K,K]*V[K]

MAT U=ZER(B,N)

PRINT K, V(K), J(K), V(K)*J(K)

MAT U=Y*W

NEXT K

MAT W=ZER[N.N]

```

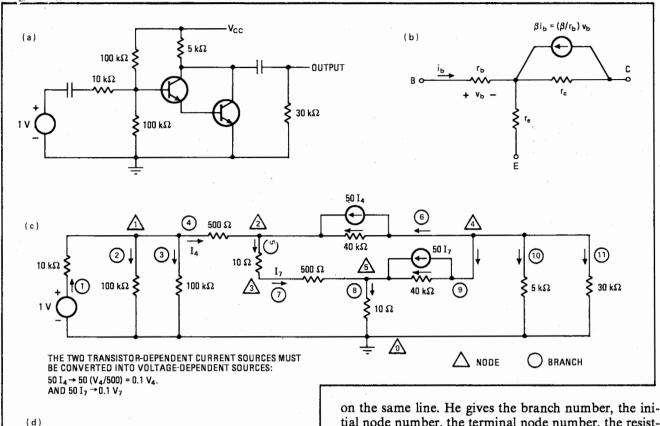

2. Program at work. The transistor amplifier in (a) is analyzed for dc conditions. The T-model equivalent circuit (b) can be used for the transistors, provided that all dependent current sources are converted into voltage-dependent sources. In the complete amplifier equivalent circuit (c), all nodes and branches are numbered consecutively. The program printout is shown in (d).

on the same line. He gives the branch number, the initial node number, the terminal node number, the resistance value, the value of the independent voltage source, the value of the independent current source, the transconductance of the dependent current source, and the number of the branch that is controlling the dependent current source, finally pressing the RETURN key.

The polarity signs allotted to the voltage and current sources must agree with the sign conventions defined by the standard branch of Fig. 1. The various data inputs must be separated by commas.

Once the program has all of the input data, it will compute the circuit's output node voltages, as well as all the branch and element voltages, currents, and power. The element of a branch is the resistance of that branch. When there is no current source associated with a branch, the branch current is the same as the element current. And when a branch does not have a voltage source, branch and element voltages are the same.

Figure 2 shows an example analysis of a two-transistor amplifier (Fig. 2a). The simple T-model equivalent circuit (Fig. 2b) is used to represent each transistor. In the complete amplifier equivalent circuit (Fig. 2c), the node numbers are enclosed by triangles, and the branch numbers are encircled. The program printout (Fig. 2d) conveniently tabulates the input data, the output node voltages, the branch data, and then the element data.

On a 16-bit minicomputer with an 8,000-word memory, the program can handle a circuit having up to seven nodes and 15 branches. If a machine with more storage capacity is used, the dimensions of the arrays set up by statement 100 in the program listing can be increased to accommodate larger circuits.

Engineer's notebook is a regular feature in Electronics. We invite readers to submit original design shortcuts, calculation aids, measurement and test techniques, and other ideas for saving engineering time or cost. We'll pay \$50 for each item published.